En la conferencia anual Hot Chips, IBM reveló detalles del nuevo Procesador IBM Telum, diseñado para llevar la inferencia de Deep Learning a cargas de trabajo empresariales para ayudar a abordar el fraude en tiempo real.

Telum es el primer procesador de IBM que contiene aceleración para la inferencia de Inteligencia Artificial (AI) desde el chip mientras una transacción se está realizando. Con tres años de desarrollo, la innovación de este nuevo chip a la aceleración del hardware está diseñada para ayudar a los clientes para obtener insights de negocio a escala en aplicaciones bancarias.

Se espera que un sistema de IBM que aprovecha Telum esté disponible en el primer semestre de 2022. En una investigación reciente de Morning Consult encargada por IBM, el 90% de los encuestados dijo que poder construir y ejecutar proyectos de Inteligencia Artificial donde residen sus datos es importante.

IBM Telum está diseñado para permitir a las aplicaciones correr eficientemente donde residen los datos, ayudando a superar los enfoques tradicionales de IA empresarial que tienden a requerir una cantidad significativa de memoria y capacidades para mover los datos para gestionar la inferencia.

De acuerdo con el Consumer Sentinel Network DataBook de 2020 de la Comisión Federal de Comercio, los consumidores informaron haber perdido más de $ 3.3 mil millones por fraude en 2020, en comparación con $ 1.8 mil millones en 2019.

Telum puede ayudar a los clientes a moverse de una postura de detección de fraude a una postura de prevención de fraude, pasando de detectar muchos casos de fraude en la actualidad, a una era potencialmente nueva de prevención de fraude a escala, sin impactar los acuerdos de nivel de servicio (SLA), antes de que se complete la transacción.

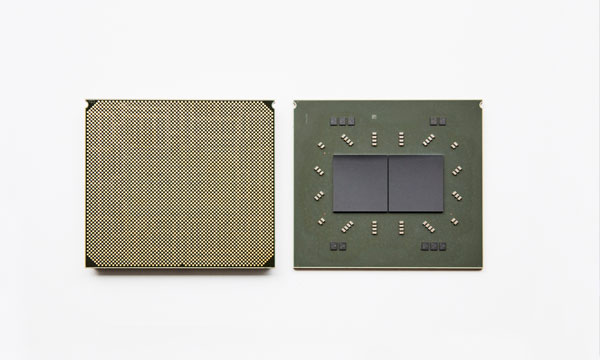

El chip contiene 8 núcleos de procesador con un pipeline profundo superescalar de instrucciones desordenadas, ejecutándose con una frecuencia de reloj de más de 5GHz, optimizada para las demandas de cargas de trabajo heterogéneas de clase empresarial.

La infraestructura de caché e interconexión de chip totalmente rediseñada proporciona 32MB de caché por núcleo, y puede escalar hasta 32 chips de Telum. El diseño del modulo dual del chip contiene 22 mil millones de transistores y 19 millas de cable en 17 capas de metal.